# Laboratory 3: Reliability Testing of Electronic Packaging

ME/MSE 487 AA/AB Autumn 2007 Electronic Packaging Laboratory

#### **OBJECTIVE**

The objective of this laboratory is to gain a firm understanding of the effects of moisture and extreme temperatures on plastic encapsulated packaging and to become familiar with reliability testing. In addition, the student will examine the design requirements of electrical conductors within electronic packages and predict the resistance of a TiW trace on a Si die.

## **INTRODUCTION**

Both elevated humidity and elevated temperature have been studied as failure factors for predicting the reliability of electronic packaging. Reliability is defined as:

The conditional probability that for a given confidence level, the product will perform as intended (i.e., without failure and within specified performance levels) for a specified mission time, when used in the manner and for the purposes intended under specified application and operational conditions. [2]

Reliability can be estimated in design, controlled in manufacturing, measured during testing and sustained in the field. Reliability is the most critical issue in plastic encapsulated electronic packaging since electronic devices are expected to perform in various environments and under various conditions without failing. The reliability of electronic packages must be further evaluated after they have been subjected to possible extreme conditions during shipping and storage.

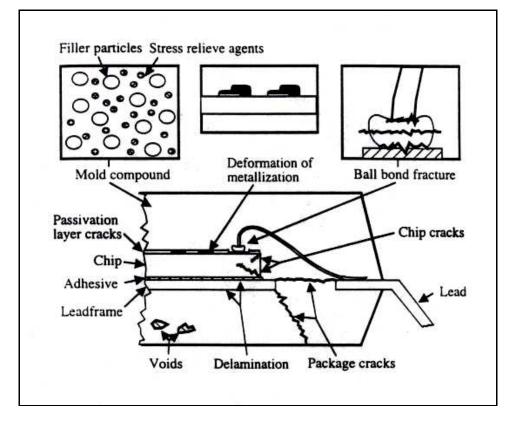

Mechanisms that cause failure of an electronic device may include any of the following: temperature, humidity, vibration, shock, pressure, electrical bias, acoustics, EMI (Electro-Magnetic Interference), and corrosives. The effects of these mechanisms can be seen in Figure 1. [1]

Extreme temperature will effect the package by causing temperature gradients with in the package components. Temperature gradients induce coefficient of thermal expansion (CTE) mismatch between die, die attach, encapsulant, and wirebonds. This CTE mismatch can cause delamination, voids, and cracks. Elevated humidity damages packaging due to corrosion and oxidation and other moisture related effects. Table 1 shows other failure modes and the mechanisms that cause or aggravate these modes. [1] Not shown in Figure 1 is the "popcorn"

type failure where the entrapped moisture can expand as steam at elevated temperatures and cause the formation of large voids in the package.

One of the most commonly performed reliability tests is to subject the package to 85% RH at 85° C for 1000 hours. This test subjects the package to conditions much worse than it will likely experience during use to allow for accelerated testing. Due to the limited time frame we will be conducting a shorter test on the order of 300-400 hours. At various point in our testing we will test the performance of our package. To do this we will monitor the resistance of our two resistors on the die. In addition to this test, we will also subject the packages to extreme temperatures to simulate possible conditions encountered during shipping. We will subject the devices to 135° C, to simulate summer shipment in a railroad boxcar through the desert, and -40° C which could be experienced either during shipment by air or during winter time surface transport. These temperatures might sound extreme, but we remember that we are performing accelerated testing, so we must use more extreme conditions.

Figure 1: Failure Sites, Failure Modes, Failure Mechanisms and Environmental Loads on a Plastic Encapsulated Packaging [1]

| Packaging Feature | Device Failure Mode                           | Failure Cause                                                                                                          | l ailure<br>Xegravating<br>Conditions                          |

|-------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Package body      | Shorting due to plating<br>flaking or peeling | Corrosion due to<br>contamination                                                                                      | Loss of hermeticity, high<br>water content, thermal<br>cycling |

|                   | Electrical leakage between<br>pins            | Contamination hydration                                                                                                | Loss of hermeticity, high<br>water content                     |

|                   | Open in lead wires                            | Fracture of bond wires                                                                                                 | Expansion of plastic<br>packaging material                     |

| Package scal      | Shorting of internal leads                    | Corrosion of package lands<br>Solder splash during lid scal<br>Lid dropped during<br>placement, crushing lead<br>wires | Contamination in package<br>Thermal cycling<br>Thermal cycling |

|                   | Chip surface leakage increase                 | Hydration of chip surface due<br>to seal break                                                                         | Mechanical shock or therm<br>eveling                           |

|                   | Chip surface leakage increase                 | Condensation of entrapped<br>moisture on chip surface                                                                  | Cold soak                                                      |

| Package leads     | Shorted leads                                 | Cracking of plating and subsequent flaking                                                                             | Humidity and thermal cycling                                   |

|                   | Open leads                                    | Corrosion and subsequent<br>flaking of plating material<br>Fractured leads due to<br>mechanical stress or stress       | Humidity and thermal<br>cycling<br>Vibration, thermal cycling  |

|                   | Bond wires opened                             | corrosion cracking<br>Solder joint cracking at board<br>due to gold embrittlement<br>Kirkendall voiding in             | Thermal cycling<br>High-temperature long-term                  |

|                   |                                               | bimetallic bonding system<br>Bond wires crushed during lid                                                             | storage<br>Thermal cycling                                     |

|                   | Bond wires shorted                            | placement<br>Wires pushed together during<br>lid placement                                                             | Thermal cycling                                                |

| Die attach        | Shorting                                      | Particulates generated during<br>die-attach move in package                                                            | Vibration and mechanical shock                                 |

|                   |                                               | Thermal runaway due to poor<br>thermal path                                                                            | High-temperature operation                                     |

|                   | Open interconnects                            | Die-attach failure causing<br>floating chip                                                                            | Thermal cycling                                                |

|                   | Electrical leakage                            | Deposition of contaminants<br>from die attach on chip<br>surface                                                       | High temperature                                               |

## Table 1 Packaging Features Impacting Reliability [2].

## **ELECTRICAL RESISTANCE PREDICTION**

The main function of an electronic package is to interconnect various electrical inputs and outputs of an integrated circuit. Thus, major design considerations for electronic packages are the minimization of electrical resistance, cross-talk, and electrical noise generation.

Typically, the electrical conductors in the integrated circuit (IC) of electronic packages are rectangular in shape. A typical IC may have many conductors of various line lengths and widths, each allowing for different current carrying abilities. The flow of current through these conductors is a result of the movement of electrons under an applied electric field. Resistance impedes the flow these electrons, and thus slows the interconnect. The resistance of a conductor is:

$$\mathbf{R} = \rho \mathbf{L} / \mathbf{w} \mathbf{t} \tag{1}$$

Where  $\rho$  is the resistivity of the conductor (material property), L is the length, w is width, and t is the thickness of the conductor. It is important to note that the resistivity value of a normal (bulk) metal is usually lower than that of a metal deposited by sputtering, evaporation, or plating (thin film).

Typically, electrical conductors in IC's are not straight but have numerous right angle bends along its path. When determining the resistance of a conductor, we often talk in terms of squares, or unit area. You will often find resistivity values reported for thin materials in units of  $\Omega/\Box$ (ohms per square). For a straight line, the number of squares is equal to the length divided by the width of the conductor. However, each right angle bend contributes only 0.56 of a square to the resistance as compared to straight squares. [2] So, for a conductor with meandering parths, equation (1) becomes:

$$R = \rho(\# \text{ of squares})/t$$

(2)

For the 2<sup>nd</sup> level package made in Lab #2, the total resistance measured using the multimeter is:

$R_{tot} = R_{TiW} + 2R_{Au \ die \ bond \ pads} + 2R_{Au \ wire} + 2R_{Package \ Leads} + 2R_{Solder \ Joints} + 2R_{Cu \ Traces} + R_{interfaces}$

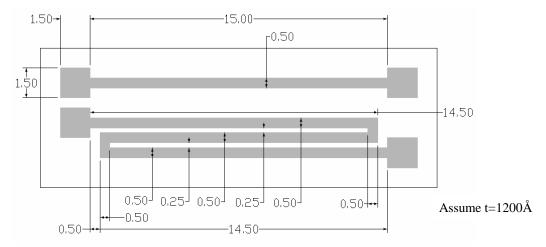

For this lab you will measure the resistance between the copper pads and you will use these values to predict the resistivity of the TiW used on the die. The dimensions of the traces on your dies are shown in Figure 2.

Figure 2. Trace dimensions on the die.

## **EXPERIMENTAL EQUIPMENT**

Completed 2<sup>nd</sup> Level Package from Lab #2

Oven/freezer

Environmental Chamber

Multimeter

Grinder/Abrasive Papers

**Optical Microscope**

Floppy disk for images

## PROCEDURE

We will perform two types of tests:

- 1. Extreme temperatures ( $135^{\circ}$  C and  $-40^{\circ}$  C).

- 2. Environmental testing (85% RH at 85° C).

Our order of testing will be:

- 1. Measure and record resistance values for your package.

- 2. The TA will load the packages in the oven (preheated to 135 °C) and let them sit for approximately 16 hours.

- 3. The packages will then be immediately transferred to the freezer (at -40° C) where they will remain overnight (between 16 and 24 hours).

- 4. After removal from the freezer the resistance values will be measured and recorded.

- 5. The packages will then be placed in the environmental chamber (85% RH at 85° C).

- 6. At several points during the environmental testing, the resistance values will be measured and recorded (due to the long duration of this portion of the test, the students will be notified by email of where and when to obtain the results).

- After environmental testing and before dissection, measure and record resistance values (this will occur during 10<sup>th</sup> week 12/4 and 12/6).

- 8. Grind and/or polish COB Package and inspect its microstructure after testing is complete.

### **ITEMS TO BE INCLUDED IN THE DISCUSSION:**

- 1. Before testing: What kinds of defects or failure modes were expected under temperature cyling test conditions?

- After testing: What defects or failure modes could you find after dissection of your COB Package?

## **QUESTIONS:**

- 1. Why are reliability tests important?

- 2. List 3 reliability tests and describe then briefly.

- 3. In order to reduce the risk of failure what should you as an electronic packaging engineer consider while designing and processing your electronic package?

- 4. Calculate the resistivity of TiW for both transmission lines. Ignore resistances (DC) due to interfaces and gold bond wire.

- 5. Does the resistance of the Au wire significantly contribute to the total resistance? Explain your answer.

- 6. Why do the measured values of resistivity for TiW differ from the "book" value of 55-75  $\mu\Omega$ cm? Give at least 2 reasons.

## References

- 1. Plastic-Encapsulated Microelectronics, M. G. Pecht, L. T. Nguyen, and E. B. Hakim, New York, John Wiley & Sons, Inc., 1995.

- 2. Physical Architecture of VLSI System, R. J. Hannemann, A. D. Kraus, and M. G. Pecht, New York, McGraw-Hill, 1989.