# MORE SHIFTY BITS

MEX - BCD CONVERTER REMASH

DOUBLE - DARBLE ALGORITHM

NAME COMES FROM OLD METHOD TO "READ" BIN ARY NUMBERS:

FOR BINARY TO BED CONVERSION, ALGORITHM

LOCKS LIKE

DSMIFT BINARY NUMBER INTO BLD REGISTER (1)

BEXAMINE EACH 4 bit group

OF OROUP 15 > 4, ADD 3

LOOP UNTIL ALL PITS ARE SMIPTED

| STRCT | 0000 | 0000 | 1101 | = D hex = 13 decimal |

|-------|------|------|------|----------------------|

| SHIFT | 0000 | 114  | 1010 |                      |

| SHIFT | 0000 | 364  | 0100 |                      |

| ADD 3 | 0000 | 0110 | 1000 |                      |

| SHIFT | 0001 | 0011 | 0000 | DONE                 |

The algorithm then iterates n times. On each iteration, the entire scratch space is left-shifted one bit. However, before the left-shift is done, any BCD digit which is greater than 4 is incremented by 3. The increment ensures that a value of 5, incremented and left-shifted, becomes 16, thus correctly "carrying" into the next BCD digit.

The double-dabble algorithm, performed on the value 243, looks like this:

| 100s                                   | Tens         | Ones | Original                         |                                                                   |

|----------------------------------------|--------------|------|----------------------------------|-------------------------------------------------------------------|

| 0010                                   | 0100         | 0011 | 11110011                         |                                                                   |

| 0000                                   | 0000         | 0001 | 11110011<br>11100110             | Initialization  Shift FIRST 3 SMIFTS NEED NO TEST                 |

| 0000                                   | 0000         |      | 11001100<br>10011000<br>10011000 | Shift                                                             |

| 0000                                   | 0001<br>0001 | 0101 | 0011000<br>00110000<br>00110000  | Add 3 to ONES, since it was 7 Shift Add 3 to ONES, since it was 5 |

| 0000                                   | 0011<br>0110 | 0000 | 01100000<br>11000000             | Shift Shift                                                       |

| 00.00                                  | 1001<br>0010 | 0000 | 11000000<br>10000000             | Add 3 to TENS, since it was 6<br>Shift                            |

| 0010                                   | 0100         |      | 0000000                          | Shift                                                             |

| 4                                      | 4<br>BCI     | 3    |                                  | LOOS MEVER LARGER THAN 2                                          |

| ************************************** |              |      |                                  | DIGIT FOR >4 CONDITION (FF = 255)                                 |

|                                        |              |      |                                  | MO11                                                              |

| MAKING IT WORK ON A PIC                       |

|-----------------------------------------------|

| PROBLEM: HOW DO YOU SMIFT ONE VARIABLE        |

| INTO ANOTHER?                                 |

| THIS WON'T WORK?                              |

| RLF binary 10010110 = 0,1001011               |

| 1111 Invace W 10 = 10010110                   |

|                                               |

| WANT BCDAG                                    |

| BUT LOOKS RLF ROTATES THROUGH CARRY &         |

| RIE F, d DUES FEFERE                          |

| TOP PIT GOD INTO C AND C GOBS INTO POTTOM PIT |

| REMEMBER : CARRY "LIVES" IN STATUS            |

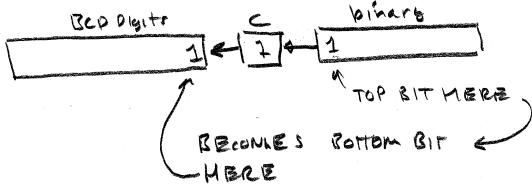

SO TWO SUCH RLP STATEMENTS DOES THE FOLLOWING:

HOW DO YOU TEST TOJEE PROPLEM: IF A GROUP OF 4 61ts HAS A NUMBER CREATER THAN 43 (THERE AME NO ">" " OPERATORS) WE CAN ONLY TEST BITS. IF WE ADD 3 TO 5, 6, 7 NOTICE WE GET 8, 9, 10 0000 0001 TOP BIT SET 0010 0011 ALGORITHM : 010064 - ADD 3 0101 <- 5 ) MOST

IMPERTANT -TEST TOP BIT L SET? KEEP ADD 3 011127 -NOTIET? DON'T KEEP ADD 3 1000687 NO0 3 THE PARTY WAS 001 SET

```

; bin contains the binary value to convert.

; Conversion process destroys contents

; Result is in bcdH, bcdL on return.

; Call bin2bcd to perform conversion.

bin2bcd

movlw

d'5'

; Setting counter to 5 because first

movwf

counter

three shifts are done without a test.

clrf

bcdL

clrf

bcdH

rlf

bin,F

; These RLFs move the left (high) bits into

rlf

bcdL, F

bcdL through the carry bit (in STATUS)

rlf

bin,F

rlf

bcdL, F

rlf

bin,F

rlf

bcdL, F

; Get bcdL into W

movfw

bcdL

repeat

addlw

0x33

; Add 3 to both low and high nibble

movwf

; Copy into temp for test

temp

movfw

bcdL

; Get bcdL into W again

; Do the test on the high bit of the low nibble.

btfsc

temp, 3

addlw

0x03

; If the low nibble > 4, then the high bit will

be set when 3 was added, so we should add 3.

btfsc

temp,7

; Now check the high bit of the high nibble

addlw

0x30

and add 3 if the high nibble is > 4

movwf

bcdL

; Copy the result back into bcdL

rlf

bin,F

; Shift bin again.

rlf

bcdL, F

rlf

bcdH, F

; Now include the shift into the high byte

; We don't need to check bcdH because with

a maximum of 255, this byte will never be

bigger than 2

decfsz

counter, F

; Decrement the counter

aoto

repeat

; repeat until the last bit of bin is shifted.

return

Finish

END

; End of program

```

# LAG PROJECT : SONIC PANGER WITH REAPOUT

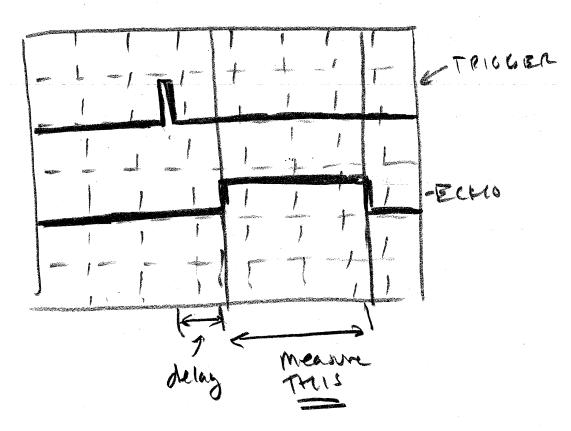

LITICK TICK TICK TICK Recall Physics IZI LABS - SONIC RANGER DEVICE - SONIC RANGER SENDS OUT ULTRASUNIC PULSES. - ECHO OF PULSES IS PICKED UP - TIME OF ECHO PROPORTIONAL TO DISTANCE US 2 SOUND SPEED V. At (-340 m/s) At = BCHO TIME d = distance SOUND TRAVELS to and From OBJECT

## TO USE SONIC RANGER, NEED

- · A TRICUER PULSE, SIOMS

- · A WAY TO MEASURE TIME OF ECHO

SIGNALS

### Manual

#### **Features**

➤ Distance measurement range: 2cm - 400cm

Accuracy: 0.3cm

Detect angle: 15 degree

Single +5V DC operation

Current comsuption: 15mA

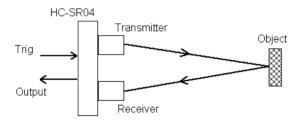

Fig. 1

#### **How It Works**

HC-SR04 consists of ultrasonic transmitter, receiver, and control circuits. When trigged it sends out a series of 40KHz ultrasonic pulses and receives echo from an object. The distance between the unit and the object is calculated by measuring the traveling time of sound and output it as the width of a TTL pulse.

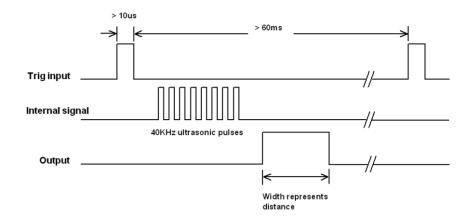

Fig. 2

#### **How To Use It**

To measure distance you need to generate a trig signal and drive it to the Trig Input pin. The trig signal leve must meet TTL level requirements (i.e. High level > 2.4V, low level < 0.8V) and its width must be greater than 10us. At the same time you need to monitor the Output pin by measuring the pulse width of output signal. The detected distance can be calculated by the formula below.

$$Distance = \frac{Pulse Width * Sound Speed}{2}$$

Fig.3

where the pulse width is in unit of second and sound speed is in unit of meter/second. Normally sound speed is 340m/s under room temperature.

Fig. 4

**Notes:** 1. The width of trig signal must be greater than 10us

2. The repeat interval of trig signal should be greater than 60ms to avoid interference between connective measurements.

#### **Specifications**

| Parameters          | Specification                              |  |  |  |  |

|---------------------|--------------------------------------------|--|--|--|--|

| Operating Voltage   | +5V DC                                     |  |  |  |  |

| Operating Current   | 15mA                                       |  |  |  |  |

| Operating Frequency | 40KHz                                      |  |  |  |  |

| Maximum Distance    | 400cm                                      |  |  |  |  |

| Minimum Distance    | 2cm                                        |  |  |  |  |

| Detect Angle        | 15 degree                                  |  |  |  |  |

| Resolution          | 0.3cm                                      |  |  |  |  |

| Input Trig Signal   | >10us TTL pulse                            |  |  |  |  |

| Output Signal       | TTL pulse with width representing distance |  |  |  |  |

| Weight              |                                            |  |  |  |  |

| Dimension           | 45 x 20 x 15 mm                            |  |  |  |  |

Copyright 2011 AccuDIY.com All rights reserved

## BASIC PLAN:

- · SET RAD AS OUTPUT, RAI AS INPUT, START TIMER

- TURN RAD ON, THEN OFF -> MAKES TEICLER

- WATT FOR ECHO PULSE TO GO HI ON RAI

- WHEN RAI GOES HIGH, ZERD TIMER

- WART

- WHEN RAI GOB! LOW, READ TIMER

- SAVE RESULT IN REGISTER

- CONVERT TO PCD DIGITS

- RISPLAY DIELTS USING PORTE AND MP DISPLAYS

- DO IT AGAIN

## TIMER? VARIOUS OPTIONS

### TIMERO

· Can use intend or external clock T LIKE WIDE PRESCALER

3 bit prescaler 7:1 -> 1:256

### TIMER 1

- 16 bit.

- . Can use Internal or Externel clock

- . 2 bit prescaler 1:1 -> 1:8

### TIMER 2

- a 8 bit

- · Internel clock only

- · Prescaler 1:1, 1:4, 1:16 only

- · Mas comparator sets interrupt flag

AT TIMER O Look SYNC DOESHT MATTER FOR FIGURE 6-1: **BLOCK DIAGRAM OF THE TIMERO/WDT PRESCALER** CLKO (= Fosc/4) Data Bus NOTE CLOCK RA4/T0CKI pin Sync 2 RUNS AT TMR0 reg Cycles INSTRUCTION T0SE T<sub>0</sub>CS Set Flag bit TMR0IF on Overflow SPEED Prescaler Foschy 8-bit Prescaler **WDT Timer** 16-bit 31.25 kHz Prescaler 8 - to - 1 MUX - PS2:PS0 PSA 🛕 WDT Enable bit WATCHOUG MUXTIMER (FOR ANOTHER DAY ... ) WDT Time-out

Note: T0CS, T0SE, PSA, PS2:PS0 are (OPTION<5:0>).

PRESCALER CAN BE USED WITH WOT OR TIMERO, PUT 10M BOTH

INTERNAL

CLOCK,

## TIMER O CONTROL REGISTER IS CALLED OPTION-REG

DMK 1 OPTION\_REG REGISTER (ADDRESS 81h, 181h) **REGISTER 6-1:** R/W-1 **R/W-1** R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 R/W-1 PS<sub>2</sub> PS<sub>1</sub> PS0 **PSA RBPU** INTEDG T0CS **TOSE** bit 0 bit 7 RBPU-P@RTB-PUIFUFEnable-b TOU USTED INTEDG: Interrupt-Edge Select bit --bit-6 TOCS: TMR0 Clock Source Select bit bit 5 1 = Transition on TOCKI pin 0 = Internal instruction cycle clock (CLKO) THERNAL CLOCK T0SE: TMR0 Source Edge Select bit bit 4 1 = Increment on high-to-low transition on TOCKI pin 0 = Increment on low-to-high transition on T0CKI pin PSA: Prescaler Assignment bit bit 3 1 = Prescaler is assigned to the WDT USES PRESCALER TIMERO 0 = Prescaler is assigned to the Timer0 module bit 2-0 PS<2:0>: Prescaler Rate Select bits Bit Value TMR0 Rate WDT Rate 1:2 1:1 000 1:2 1:4 001 1:4 1:8 010 1:8 011 1:16 1:32 1:16 100 1:64 1:32 101 1:128 1:64 110 1:256 1:128 111 Legend: U = Unimplemented bit, read as '0' R = Readable bit W = Writable bit x = Bit is unknown '0' = Bit is cleared '1' = Bit is set n = Value at POR

| TABLE 6-1: | DECISTERS | ASSOCIATED | WITH TIMER0      |

|------------|-----------|------------|------------------|

| IABLE 0-1: | REGISTERS | ASSUCIATED | AAIIII IIIAILIZO |

BANK O

BANK I

|   | Address               | Name   | Bit 7     | Bit 6       | Bit 5  | Bit 4 | Bit 3 | Bit 2  | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>RESETS |               |

|---|-----------------------|--------|-----------|-------------|--------|-------|-------|--------|-------|-------|----------------------|---------------------------------|---------------|

| > | 01h,101h              | TMR0   | Timer0 Mo | dule Regist | er     |       |       |        |       |       | XXXX XXXX            | uuuu uuuu                       | & FOR ANOTHER |

| - | 0Bh,8Bh,<br>10Bh,18Bh | INTCON | GIE       | PEIE        | TMR0IE | INTE  | RBIE  | TMR0IF | INTF  | RBIF  | 0000 000x            | 0000 000u                       | & TOAY        |

| 4 | 81h,181h              | OPTION | RBPU      | INTEDG      | T0CS   | T0SE  | PSA   | PS2    | PS1   | PS0   | 1111 1111            | 1111 1111                       |               |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by Timer0.

## CHOOSING TIMER PARAMETERS ECHO PULSE PROPORTIONAL e At TO DISTANCE - DIGITAL DISPLAY = 2 DIGITS , 00 - 99 - FOR LAB RENCH DEVICE, HAVING I disit & I cm SPEMS REASONABLE WHAT IS BE FOR I CM? d = v, At = 2d = (2)(0,01 m) D= 1340 m/s) = 0,0588 ms THIS corresponds to 17,000 Hz A TIMER CLOCK FREQUENCY

FUR

# WANT TIMERO CLOCK TO BE CLOSE TO F,000HZ NOTE, WITH IMSTRUCTION CYCLE:

| TIMERO CLOCK | PRESCALER    |

|--------------|--------------|

| IMUZ         | 1            |

| 500 KM+      | 2            |

| 250 kH7      | 4            |

| 125 kHz      | 8<br>16      |

| 62,5 hHz     | 32           |

| 15, 625 kHz  | 64 & CLOSEST |

| 7. 8125 hHz  | 128          |

OK FOR FIRST ATTEMPT

```

list F=inhx8m, P=16F88, R=hex, N=0; File format, chip, and default radix

#include p16f88.inc; PIC 16f88 specific register definitions

config CONFIG1, FOSC INTOSCCLK & WDT OFF & LVP OFF & PWRTE OFF &

BODEN ON & LVP OFF & CPD OFF & WRT PROTECT OFF & CCP1 RB0 & CP OFF

config CONFIG2 , IESO OFF & FCMEN OFF

; You may want to add other variables here

CBLOCK 0x20

TimerCounts; Saving timer counts

; used in bin2bcd

; used in bin2bcd

bcdH

bcdL

; used in bin2bcd

counter ; used in bin2bcd

temp

; used in bin2bcd

ENDC

; RAM preserved ------

; Program Memory -------

org 0

goto

Init

; Interrupt Service Routine ------

; ISR beginning

org

; Microcontroller initialization

org 8

; Set Internal oscillator as you choose

SetOSC

; Set up I/O on PORTA<0> Output, PORTA<1> input and PORTB<7:0> output

; Set up TimerO, using OPTION REG

SetTimer

```

```

MainLoop

; Make 10 microsecond pulse on PORTA<0>

Pulse

; Wait until PORTA<1> Goes HI, then clear TMR0

PulseWait and Clear

; Wait until PORTA<1> Goes LOW, then read TMR0 into W

EndEchoWait and Read

; Save TMRO and pass to BCD converter and then display

movwf TimerCounts ; Save for debug comparison

movwf bin

; Save TMR0 to bin for Convertion

call bin2bcd

call UpdateDisplay

call Delay

; Wait so we don't pulse too fast

goto MainLoop

; Time Waster Routine

Delay

; Display output routine. Checks to see if there is a digit above "99"

If so, it outputs an overflow "OF" indication.

UpdateDisplay

movf bcdH, w

;Set Status 0 Flag

btfss STATUS, Z

goto Overflow

;Send OF to register if we've overflowed

movf bcdL, w

movwf PORTB

return

Overflow

movlw H'OF'

movwf PORTB

return

; Include the binary to BCD converter here

#include bin2bcd.inc

Finish

end

; end of program

```

; Main part of loop