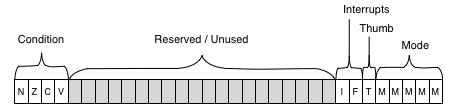

Current Program Status Register (CPSR)¶

The status register bits.

Condition Bits¶

N

- Is set to bit 31 of the result of the instruction.

- If this result is regarded as a two’s complement signed integer, then N = 1

- If the result is negative and N = 0 if it is positive or zero.

Z

- Is set to 1 if the result of the instruction is zero and to 0 otherwise.

- This often indicates an equal result from a comparison.

C

- Is set in one of four ways:

- For an addition, including the comparison instruction CMN, C is set to 1 if the addition produced a carry (that is, an unsigned overflow), and to 0 otherwise.

- For a subtraction, including the comparison instruction CMP, C is set to 0 if the subtraction produced a borrow (that is, an unsigned underflow), and to 1 otherwise.

- For non-addition/subtractions that incorporate a shift operation, C is set to the last bit shifted out of the value by the shifter.

- For other non-addition/subtractions, C is normally left unchanged (but see the individual instruction descriptions for any special cases).

V

- Is set in one of two ways:

- For an addition or subtraction, V is set to 1 if signed overflow occurred, regarding the operands and result as two’s complement signed integers.

- For non-addition/subtractions, V is normally left unchanged (but see the individual instruction descriptions for any special cases).

Mode Bits¶

MODE

- 5 bits that control what mode the CPU is in.

| M[4:0] | Mode | Accessible registers |

|---|---|---|

| 10000 | User | PC, R14 to R0, CPSR |

| 10001 | FIQ | PC, R14_fiq to R8_fiq, R7 to R0, CPSR, SPSR_fiq |

| 10010 | IRQ | PC, R14_irq, R13_irq, R12 to R0, CPSR, SPSR_irq |

| 10011 | Supervisor | PC, R14_svc, R13_svc, R12 to R0, CPSR, SPSR_svc |

| 10111 | Abort | PC, R14_abt, R13_abt, R12 to R0, CPSR, SPSR_abt |

| 11011 | Undefined | PC, R14_und, R13_und, R12 to R0, CPSR, SPSR_und |

| 11111 | System | PC, R14 to R0, CPSR |