Status Register Instructions¶

You can switch modes by calling either the MSR or the MRS instructions. These instructions either read or write the mode bits in the CPSR register.

Changing the mode does not affect interrupts. If you want to disable interrupts at the same time that you change mode you need to also change the F and I interrupt bits in the CPSR.

MRS - Move to Register from Status¶

MRS is use to read from either the CPSR or from the SPRS. It move the value from the status register into a regular register.

The SPSR that will be read is the one that is active for the CPU’s current mode.

Example:

MRS R0, CPSR

MRS R1, SPSR

Note

Reading the SPSR while in user or system mode is not valid and yields unpredictable results.

MSR - Move to Status from Register¶

The MSR instruction is used to write to the CPSR or the SPSR of the current mode.

Warning

Writing to the SPSR while in the user or system mode is not valid and the results are not predictable.

Any writes to the CPSR in user mode are ignored. The CPSR can only be written to in a priveleged mode.

Example:

MSR CPSR, R0

MSR SPSR, R1

MSR Field Masks¶

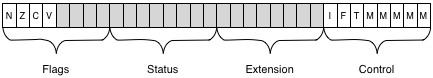

The status register field flags.

The MSR instruction can use the immeditate addressing mode. And to make the instruction more efficient it can be modified with field flags.

These field codes create a mask so that one can change only the part of the CPSR or SPSR instead of overwritting the whole register. The flags divide the status registers into 4 one byte pieces allowing each piece to be updated independently.

For example to set all the flags:

MSR CPSR_f, #0xF0000000

To update all the fields at once, the value must come from a register.

Note

There are some restriction as on the immediate value. It must be between 0x0 and 0xFF or an even shift left of that range.

Another way to update specific bits without affecting the value of the other bits in the status register is to first read the status register, modify the value, then write it back. For example:

MRS R0, CPSR

BIC R0, R0, #0x1F

ORR R0, R0, #0x12

MSR CPSR_c, R0

One reason to use the longer method of changing the status register is to ensure one’s code is compatible with other ARM core architectures. The sequence above ensures you only change the bits you intend to change leaving all the other ones unaffected.

Note

In user mode any writes to the priviledged or execution state bits of the CPSR are ignored.

Accessing the SPSR when in user mode or in system mode is unpredictable.

Warning

The thumb (T) or J bit should not be changed with the MSR instruction. The results are unpredictable.